Objetivos Ementa Livros Professores: JOSEANA ELMAR

|

Guia de LaboratórioUma interface foi escolhida para facilitar aprendizagem e simplificar acompanhamento de seus projetos.

Considere um Circuito a Fazer (CAF) como sendo qualquer um (combinatório, sequencial, processador, etc) que vocę terá que implementar. [Ver observaçőes] =]

De um lado, chaves escrevem 02 palavras = Entrada do CAF. [Ver figura abaixo]

Na saída, HEX7-0, LEDR, LEDG, e LCD = SAÍDA do CAF.

No meio, sua lógica irá operar entrada e produzir saída.

Ambiente de Verificaçăo ObrigatóriaObservaçőesCopie a pasta /labarc/DE2_TOP para seu home. O livro é essencial para conseguir fazer esses laboratórios. Priorizar compreensăo e completude da interface. Assim que ela estiver verificada e validada por vocę, dedique sua atençăo integral ao CAF. Leite para o display de 7 segmentos: pasta Leite para o LCD: Layout da Interface da ULASimplificaçăo: desconsidere o sinal C (carry out). EntradaBotőes KEY: Chaves de Execuçăo

KEY0 - (livre)

KEY1 - (livre)

KEY2 - (livre)

KEY3 - (livre)

Chave SW[17] : (livre)

Chave SW[16] : Modo=0 ou Modo=1 setado pelo usuário

Ou seja, alimenta 2 buffers na entrada do CAF

Chaves SW[15:0] : Dados de entrada setados pelo usuário

Modo 0: dados a serem aplicadas para entradas de controle

15:9 - (livre)

8:6 - S[2:0]

5 - Cin

2:0 - (livre)

Modo 1:

15:8 - dados a serem aplicadas para entrada A

7:0 - dados a serem aplicadas para entrada B

SaídaLCD - 2 linhas com 5 valores de 8 bits em cada linha

Displays de 7 segmentos: 2 valores de 8 bits e 1 valor de 16 bits

LEDS

Verdes LEDG:

8 (no meio dos display de 7 segmentos) - (livre)

7:0 - (livre)

Vermelhos LEDR: Visualizam dados de entrada e sinais internos

17:9 - (livre)

8:6 - S[2:0]

5 - Cin

2:0 - (livre)

Layout da Interface do DatapathErrata: no livro, na Table 9-4, no lugar de "Select[3:0]" deve-se ler "Select[1:0]". Simplificaçăo: desconsidere o sinal V (overflow) e C (carry out). EntradaChaves KEY: Chaves de Execuçăo

KEY0 = (livre)

KEY1 - (livre)

KEY2 - (livre)

KEY3 - reset

Chave SW[17] : pushando essa chave, o clk pára de oscilar

Chave SW[16] : Modo 0 e Modo 1 setado pelo usuário

Ou seja, alimenta 2 buffers na entrada do CAF

Chaves SW[15:0] : Dados de entrada setados pelo usuário

Modo 0: dados a serem aplicadas para entradas de controle

15:14 - Destination select

13:12 - A select

11:10 - B select

9 - MB select

8:5 - G select

4:3 - H select

2 - MF select

1 - MD select

0 - Load_enable

Modo 1:

15:8 - dados a serem aplicadas para entrada Constant in

7:0 - dados a serem aplicadas para entrada Data in

SaídaLCD - 2 linhas com 5 valores de 8 bits em cada linha

Displays de 7 segmentos:

LEDS

Verdes LEDG:

8 (no meio dos display de 7 segmentos) - clk de 0,5 Hz (período de oscilaçăo de 2 segundos)

7 - Z - Zero

6 - N - Negative

5:0 - (livre)

Vermelhos: LEDR:

17:16 - (livre)

15:14 - Destination select

13:12 - A select

11:10 - B select

9 - MB select

8:5 - G select

4:3 - H select

2 - MF select

1 - MD select

0 - Load enable

Para levar para fora do datapath valores que năo sao verdadeiras saídas do datapath, deve-se usar a seguinte definiçăo de tipo: typedef struct { logic [W-1:0] R [0:(1<<M)-1];

logic [W-1:0] BusD, G, H; } visual_dp_t;

sendo que Casos de Teste MUX B: Constant_in=0x5A MBselect=1; 0x5A em Data_out

MUX D: Data_in=0x32 MDselect=1; 0x32 em BusD

R2: BusD=0x32 Load_enable=1 Destination_select=2; 0x32 em R2

ALU: R2=0x32 BusB=0x5A Aselect=2 Gselect=2; 0x8C em G e Z=0 N=1; MFselect=0 MDselect=0; 0x8C em BusD

Shifter: BusB=0x5A Hselect=1; 0x2D em H; MFselect=1 MDselect=0; 0x2D em BusD

Z: reset; Z=1

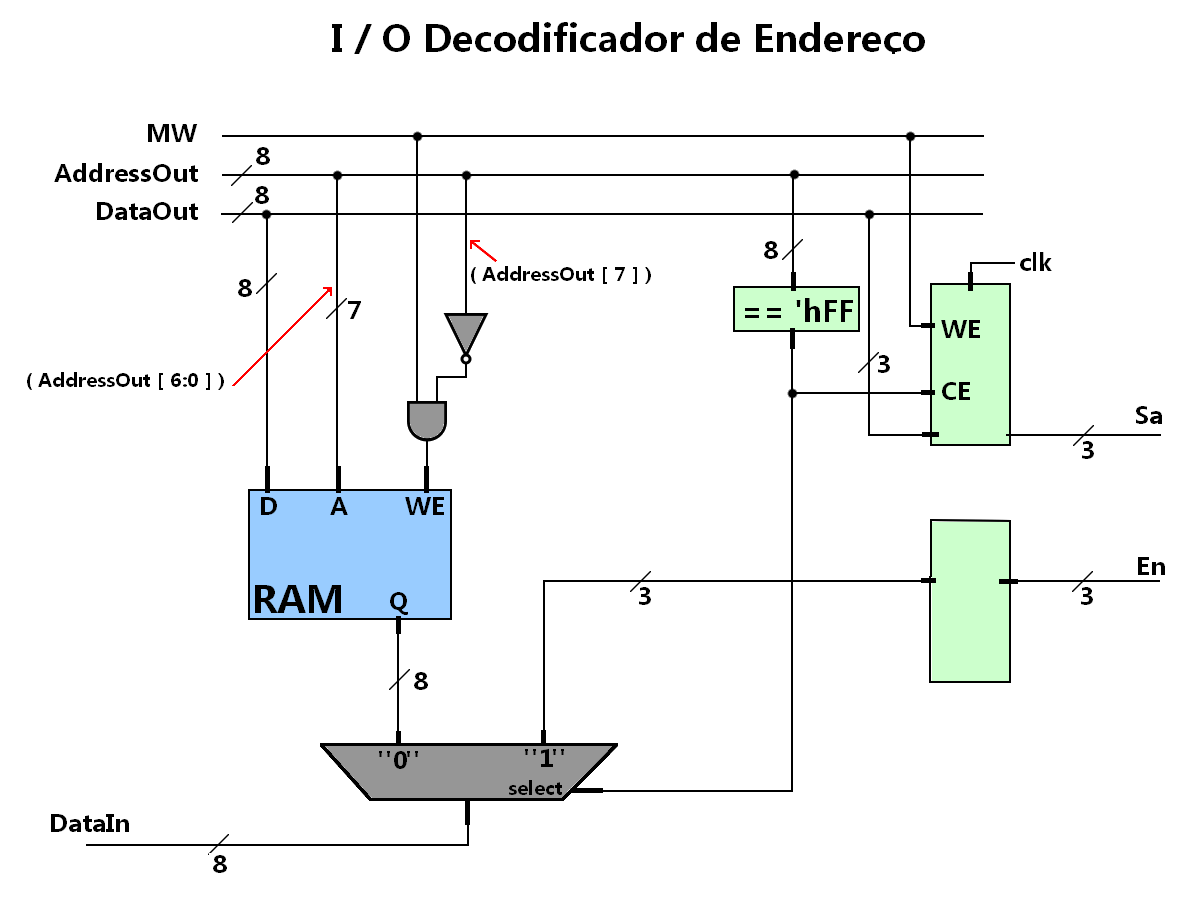

CPU - Processador com Memória e IO LegendaProcessadorDataOut

Dado a ser enviado para fora do processador.

DataIn

Dado a ser enviado para dentro do processador.

MW - Memory Write

Saída do processador sinalizando que tem dados a serem recebidos em DataOut.

Address

Endereço para o qual o valor do DataOut está sendo enviado ou de onde o valor para DataIn deve ser buscado.

Address == 'hFF seleciona o dispositivo de entrada/saída.

Address entre 'h00 e 'h7F seleciona a memória.

RAMD entrada de dados

Q saída de dados

A entrada de endereço

WE - Write Enable

Sinaliza ŕ RAM para receber o dado em D e armazenar no endereço A.

Entrada \ Saida (Input \ Output)WE - Write Enable

Sinaliza que o dado é válido para Saída.

CE - Chip Enable

Se o valor de Address for 'hFF o DataIn receberá o valor da entrada (input).

Se năo, o DataIn receberá o valor da saída Q da RAM.

Layout da Interface da CPUEntradasChaves KEY: Chaves de Execuçăo

KEY0 - (livre)

KEY1 - (livre)

KEY2 - (livre)

KEY3 - reset

Chave SW[17] : pushando essa chave, o clk pára de oscilar

Chave SW[16] : Modo 0 e Modo 1 setado pelo usuário

Chaves SW[15:0] : Entrada de interrupçăo do processador e Entradas da CPU

SaídasLCD - 2 linhas com 5 valores de 8 bits em cada linha

Modo 0:

Displays de 7 segmentos:

LEDS

Verdes LEDG:

8 (no meio dos display de 7 segmentos) - clk de 0,5 Hz (período de oscilaçăo de 2 segundos)

7 - Z - Zero

6 - N - Negative

5 - PL

4 - JB

3 - BC

2:0 - Sa[2:0] - Saídas da CPU

Vermelhos LEDR: Control word

17 - busy - da cache

16 - MW - bit 3 do control word conforme Figura 9-16 do livro

15:13 - DA

12:10 - AA

9:7 - BA

6 - MB

5:2 - FS

1 - MD

0 - RW

Para levar para fora do processador valores que năo sao verdadeiras saídas do processador, deve-se usar a seguinte definiçăo de tipo: typedef struct { logic [W-1:0] pc, constant_in;

logic [15:0] instruction;

logic [19:0] control_word;

logic z, n;

visual_dp_t dp; } visual_pr_t;

Casos de TesteSupersimplesINC R1,R1 INC R1,R1 DEC R1,R1 DEC R1,R1 Carregamento_imediatoLDI R1,5 LDI R2,1Ah ; usando bits 5:0 da instrucao LDI R2,9Ah ; usando bits 10:9 e 5:0 da instrucao ADI R3,R1,4 PulandoLDI R1,5 BRZ R1,30 LDI R2,0 BRZ R2,2 LDI R1,0 INC R1,R1 LDI R3,1 JMP R3 Escrita_leituraLDI R2,2 LDI R3,7 ST R2,R3 ; store value 7 at memory address 2 ST R3,R2 ; store value 2 at memory address 7 LD R0,R3 ; read value from memory address 7, which is 2, into R0 LD R1,R2 ; read value from memory address 2, which is 7, into R1 SaidaLDI R3,0 DEC R3,R3 LDI R2,2 ST R3,R2 ; send value 2 to output Sa EntradaLDI R3,0 DEC R3,R3 LD R0,R3 ; get input value from En into register R0 Veja também Dicas Quartus |