Objetivos Ementa Livros Professores: JOSEANA ELMAR

|

Informaçőes preliminares sobre conceitos básicos de matematicaNo exercício anterior escondemos propositalmente a motivaçăo para todas aquelas operaçőes de divisăo, para que vocęs pudessem se concentrar somente na divisăo em si. Agora, finalmente, vamos revelar os "porquęs". O quę é esse numero chamado π ?Veja este vídeo, especialmente a cena na qual o professor está movimenta a bicicleta dele na garagem dele. O quę é uma série ?O quę significa a palavra "convergir" ? Veja este vídeo. Motivaçăo do uso de representaçăo hexadecimalVeja no final do guia do exercício de display de 7 segmentos. Série de Leibniz para ππ = 4/1 - 4/3 + 4/5 - 4/7 + ... A série de Leibniz converge para o valor de π. Calculamos pedaços da série de LeibnizDefinimos a variável vn: vn = m/a - m/(a+2) + m/(a+4) - m/(a+6) +... , a ∈ 2ℕ-1, n ∈ { 2, 4, 6,... } com m = 4*t, m ∈ ℕ, t ∈ { 16, 162, 163, 164,... } Notas para a aula do cálculo de elementos da série de LeibnizÉ preciso atribuir parâmetros com nomes significativos ŕ quantidade de bits por dígito hexadecimal e ao numerador dos elementos da série de Leibniz. Estes parâmetros precisam ser usados no código de maneira sistemática. Nenhuma linha do arquivo de código pode ter mais do que 80 caracteres, espaços inclusos. As respostas ŕs perguntas devem estar escritos em comentário dentro do código Systemverilog. As duas linhas do display LCD devem ser usadas para visualizar dígitos do resultado, iniciando na primeira linha.

Năo é possível obter uma nota de 1/2, é preciso juntar 2 questőes que valem 1/2 para ganhar nota 1. Nesta questăo, a palavra "divisor" significa "circuito de divisăo" e "dígitos" sempre se refere a dígitos hexadecimais. A expressăo "cabem" se refere a "aproveitar pelo menos 80% da FPGA". "Implemente." quer dizer que vocę precisa mostrar o resultado no display LCD da placa FPGA e ao mesmo tempo no PC usando o programa pi.py O sintetizador só sintetiza divisores de até 64 bits quando usamos o operador /. Podemos usar uma instância de um divisor combinatório que funciona para qualquer quantidade de bits dos argumentos. Instancie-o assim:

divi_comb #(.NBITS_DEND( ), .NBITS_SOR( ), .NBITS_Q( )) d1 (.dend( ), .sor( ), .q( ));

^ ^ ^ ^ ^ ^

| | | | | |

quantidade de bits do dividendo

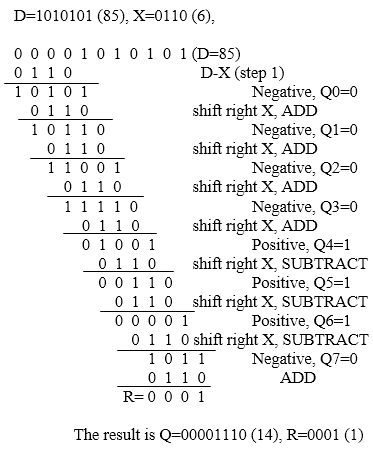

Năo é preciso copiar nenhum arquivo. Com Para quem quer saber detalhes sobre a implementaçăo deste divisor, segue uma cópia da figura 1, incluíndo um parágrafo explicativo, do trabalho "Translation of Division Algorithm into Verilog HDL", Yusmardiah et alii, ARPN Journal of Engineering and Applied Sciences, Vol. 12, No. 10, may 2017: "Assume that we have dividend, D and divisor, X as an input data, quotient, Q as division result and R as remainder. The steps of the non-restoring algorithm are calculated as visible in Figure-1."  Repare no entanto que o resultado Q deveria ser 0001110, ou seja, só 7 bits. Se for mesmo 8 bits, o resultado correto seria 00011100.

A primeira página deste documento foi usado para fazer os vídeos acima. |