Identificaçăo de Faces em Vídeo de Alta Resoluçăo

Motivaçăo: Mesmo trabalhos recentes (Spagnolo, Fanny & Perri, Stefania & Corsonello, Pasquale. (2020). Design of a real-time face detection architecture for heterogeneous systems-on-chips. Integration. 74. 10.1016/j.vlsi.2020.04.008.) trabalham com resoluçőes baixas, no caso, 320×240, comparada ŕ resoluçăo 1920×1080 de câmeras de vídeo de relativamente baixo custo. Câmeras com maior resoluçăo tem a vantagem de captar uma cena maior para uma dada quantidade de pixels por objeto observado.

Objetivo: Implementar uma soluçăo que capture vídeos em resoluçăo full-HD (1920x1080@30fps) e que seja capaz de fazer a detecçăo de faces humanas on-line (streaming).

Características de desempenho: todas as imagens fornecidas pela câmera devem ser processadas e a energia consumida pelo processamento deve ser pequeno de forma a năo se ter necessidade de resfriamento forçado (ventilador).

Algoritmo: Viola-Jones. O algoritmo Viola-Jones prevę o escalonamento da imagem por sub-amostragem, iniciando com a escala 1:1 (resoluçăo 1920x1080), depois 1:1.2, 1:1.44,... até a imagem escalonada chegar ao tamanho de 1 janela. O algoritmo Viola-Jones usa classificadores que eliminam janelas da imagem que năo săo considerados faces. O conjunto inicial de janelas é composto por todos os quadrados de tamanho de 25x25 pixels que podem ser formados a partir da imagem escalonada a ser analisada, incluindo todas as janelas parcialmente sobrepostas. O algoritmo usa classificadores que eliminam janelas que năo contém faces, até que, idealmente, só estiveram sobrando janelas contendo face. Os classificadores estăo agrupados em 25 estágios.

Implementaçăo de referęncia: Comaschi, F. (2012).Technische Universiteit Eindhoven. A implementaçăo em FPGA está sendo feita de forma a identificar, nos imagens de teste, exatamente as mesmas 911 faces que a implementaçăo da TU Eindhoven identifica, com uma tolerância de 1 pixel + 2% na posiçăo e no tamanho. Năo foi feito nenhum estudo quanto ŕ taxa de acerto ou ŕ taxa de erro da implementaçăo da TU Eindhoven, nem planejamos fazer tal estudo no futuro.

Para facilitar o uso da implementaçăo de referęncia no trabalho da depuraçăo da implementaçăo FPGA, foram feitas pequenas modificaçőes no código.

Apresentaçăo da plataforma usada

Implementaçăo em FPGA: Até o momento temos implementado 9 escalas e 6 estágios.

Publicaçőes:

Energy Consumption Measurement of a FPGA Full-HD Video Processing Platform

Errata: 74.25 MHz instead of 148.59 MHz

DPVSA 2020 (4th IEEE SPS/CASS Seasonal School on Digital Processing of Visual Signals and Applications) Poster e Video da apresentaçăo

Monteiro, H.A., Brito, A.V.d. & Melcher, E.U.K. Image normalization in embedded systems. Journal of Real-Time Image Processing (2021). https://doi.org/10.1007/s11554-021-01098-8

Laboratório Remoto para Ensino

RISC-V

Contributor #7 emelcher desde 16/9/21

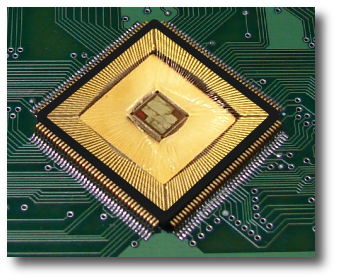

PLCM Chip

Power Line Communication Modem IP-Core (PLCM) é um projeto desenvolvido desde 2012 pelo LAD no âmbito do programa federal Brazil-IP.

Objetivo: Desenvolver um IP-core que implemente as funcionalidades da camada física de um sistema de comunicaçăo PLC (comunicaçăo pela rede elétrica) em banda estreita.

Descriçăo: O IP-core implementará métodos de modulaçăo e demodulaçăo totalmente digitais, de modo que uma interface analógica mínima seja necessária para seu uso. Além disso, ele deverá lidar com os efeitos do ruído no canal, implementando esquemas de detecçăo e correçăo de erros. Como esquema de modulaçăo, planeja-se utilizar o S-FSK, segundo especificado no padrăo IEC 61334-5-1.

Aplicaçăo: O IP-Core poderá ser usado como parte de um sistema inteligente de monitoramento de consumo energético ou de automaçăo residencial. Nesse caso, poderia ser acionado por um processador que implemente as camadas mais altas do sistema de comunicaçăo.

Fase atual do projeto: Desenvolvimento.

SPVR Chip

Notícias Relacionadas:

MPEG-4 Chip

Notícias Relacionadas:

DengueChip (Dengue é diagnosticada em questăo de minutos)

http://criadigital.com.br/denguechip

eTBc (Easy TestBench Creator)

Visăo Geral

BVM - Metodologia de Verificaçăo Funcional para Brazil-IP

Descriçăo: BVM surgiu de VeriSC e é uma metodologia de verificaçăo funcional, para circuitos digitais síncronos, através da comparaçăo do DUV com seu modelo de referęncia, permitindo a criaçăo do testbench antes mesmo da implementaçăo do DUV de forma a facilitar a verificaçăo do mesmo e dando ęnfase ŕ fase de verificaçăo.

Objetivo: A metodologia se propőe a minimizar o tempo total de verificaçăo e encontrar erros mais cedo, quando o DUV começa a ser implementado Além disso, essa metodologia propőe o reuso dos próprios elementos do testbench para criar os testbenches hierárquicos e para testar os próprios componentes do testbench e assegurar que eles năo contenham erros.

Fase do Projeto: Em contínuo desenvolvimento.

PROBRAL

Em colaboraçăo com o KIT e projeto visa a criaçăo de um ambiente heterogęneo de simulaçăo de sistemas.

Concluído.

USB sem NIOS

Descriçăo: Implementaçăo de um processador dedicado para comunicaçăo com dispositivos USB.

Objetivo: Prover comunicaçăo com dispositivos USB conectadas ŕ placa DE2 gastando menos do que 10% dos recursos do FPGA e sem utilizar memória externa ao FPGA.